# Reconfigurable Advanced Rapid-prototyping Environment (RARE):

A Computing Technology for Challenging Form Factors

Prepared by Michael J. Bonato Colorado Engineering, Inc. for HPEC 2012 September 12, 2012

#### **SBIR DATA RIGHTS**

Contractor Name: Colorado Engineering Inc. (CEI)

Contractor Address: 1310 United Heights, Suite 105, Colorado Springs, CO 80921

Expiration of SBIR Data Rights: Expires 5 years after completion of project work for this or any follow-on SBIR contract, whichever is later.

This presentation contains data developed by Colorado Engineering under SBIR contract HQ0006-08-C-7908. The Government's rights to use, modify, reproduce, release, perform, display, or disclose technical data or computer software marked with this legend are restricted during the period shown as provided in paragraph (b)(4) of the Rights in Noncommercial Technical Data and Computer Software - Small Business Innovation Research (SBIR) Program clause contained in the above identified contract. No restrictions apply after the expiration date shown above. Any reproduction of technical data, computer software, or portions thereof marked with this legend must also reproduce the markings.

Export or re-export of CEI products may be subject to restrictions and requirements of US export laws and regulations and may require advance authorization from the US Government.

#### Outline

- Background

- Overview of RARE Architecture

- Approach

- Features

- Software and Programming Model

- Packaging

- Application Examples

- Summary

### Background

- Ideal high performance computing environment is heterogeneous

- Variety of processing technologies

- General purpose / multi-core

- Field Programmable Gate Arrays (FPGAs)

- Graphics processors

- Application Specific Integrated Circuits (ASICs)

- Enables engineer to optimize solution to fit Size, Weight, and Power (SWaP) budget

- Technologies represent different points in trade space

- Computing horsepower

- Power consumption

- Programmability

### Background

- Heterogeneous computing approaches have traditionally relied on backplanes

- Added weight, size, and cost

- Constrain incremental scalability

- Backplanes limit designer's ability to realize solutions in physical volumes not conducive to legacy form factors

Image courtesy of Elma Bustronic

Image courtesy of Kontron

### A New Approach

- MDA funded an SBIR Phase I and II program to address challenges of modularity, scalability, and heterogeneity in deployments with challenging form factors

- RARE: Reconfigurable Advanced

Rapid-prototyping Environment

- Executed by CEI under technical guidance and influence of NRL, NSWC, and ONR

- Recipient of 2011 Tibbetts Award

- No Backplane!

- Presentation will describe architecture and provide real-world application examples

# MOSA Inspired Technology

- Decomposes a system into functional <u>COTS</u> <u>building blocks</u>

- Blocks provide a modular way to achieve loosely coupled <u>common</u> <u>operational subsystem</u> components

When tied together using well defined interfaces, blocks form a <u>complete</u>, <u>scalable processing</u> and <u>control system</u>

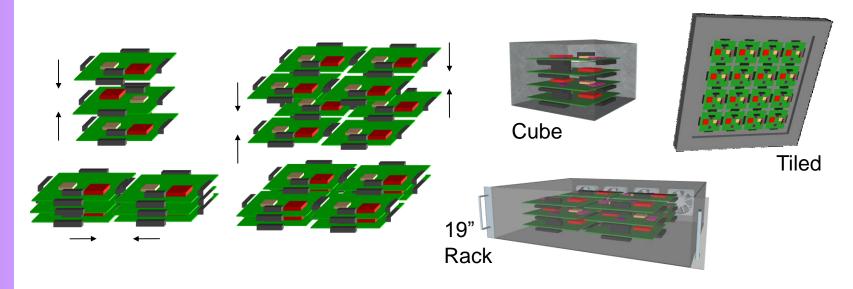

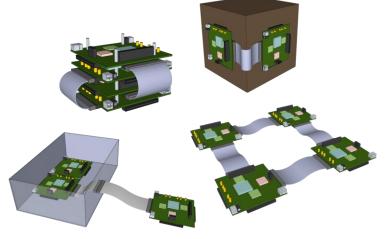

# RARE Modularity and Scalability

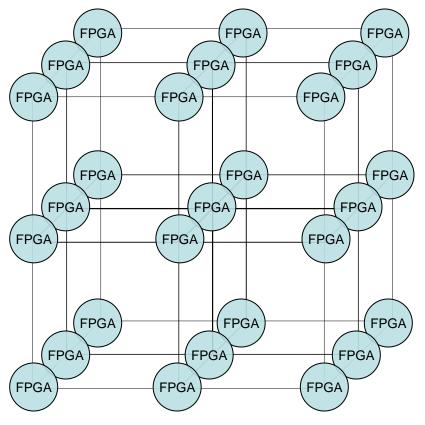

- 6.25" x 6.25" cards with interface connections in three dimensions

- I/O bandwidth of <u>39 GB/sec</u> per module via PCIe, LVDS, and SerDes

- 3D direct connectivity of FPGA processing elements

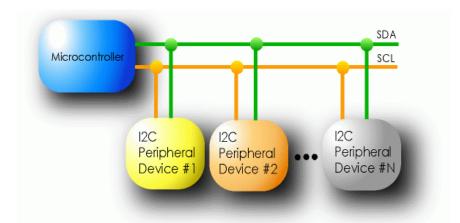

- I<sup>2</sup>C network of microcontrollers for <u>health and status management</u>

- Stack and/or tile modules in x, y, and z

- Incrementally scale performance, I/O bandwidth, and physical footprint

- Physically <u>reconfigure</u> systems while maintaining common HW/FW/SW

- Solutions in a <u>fraction of the volume</u> of traditional backplanes

# COTS Modules: Digital and RF

TRLs as of 4/5/12

#### **GP/FPGA Processor**

TRL 8

Starter Kit

- AMCC 460SX PowerPC

- Xilinx Virtex-6 FPGA

- **Dual 1Gb Ethernet**

- USB, RS-232

#### **ADC+Processor**

TRL 8

- 10 ADC channels

- 16b @ 160MSPS

- Xilinx Virtex-6 FPGA

#### **DAC+Processor**

TRL 8

- 2 DAC channels

- 16b @ 1GSPS

Xilinx Virtex-6 FPGA

**Phased Array** Antenna / Radar TRL 8 Interface

**High Fidelity, Low Phase Noise Clock Distribution**

TRL 8

TRL8

#### **PCle Expansion**

TRL 8

#### Roadmap

- Stratix V

- Multicore GP

- GPU + x86

- Ultra-wideband ADCs

- **Enhanced Tamper Resistance**

**RF Down** Converter

TRL 8

#### RARE Inter-Module I/O Bandwidths

| RARE<br>Connector | Half Duplex (FPGA LVDS @ 1GHz) |                       |                         |                         | Full Duplex            |                       |                          |                              |

|-------------------|--------------------------------|-----------------------|-------------------------|-------------------------|------------------------|-----------------------|--------------------------|------------------------------|

|                   | # of<br>Clusters               | # of<br>LVDS<br>Pairs | LVDS<br>Total<br>(Mb/s) | LVDS<br>Total<br>(MB/s) | PCIe<br>FPGA<br>(MB/s) | PCIe<br>PPC<br>(MB/s) | SerDes<br>FPGA<br>(MB/s) | Bandwidth<br>(per Connector) |

| X                 | 3                              | 7                     | 21,000                  | 2,625                   | 2,000                  | 2,000                 | 0                        | 6.625 GB/s                   |

| Y                 | 3                              | 7                     | 21,000                  | 2,625                   | 0                      | 2,000                 | 0                        | 4.625 GB/s                   |

| Z                 | 2                              | 13                    | 26,000                  | 3,250                   | 2,000                  | 2,000                 | 1,000                    | 8.250 GB/s                   |

| RARE Connector | Total Bandwidth<br>(Dual Connectors<br>per Direction) | Total Bandwidth<br>per RARE Module |  |

|----------------|-------------------------------------------------------|------------------------------------|--|

| X              | 13.25 GB/s                                            |                                    |  |

| Y              | 9.25 GB/s                                             | 39.00 GB/s                         |  |

| Z              | 16.50 GB/s                                            |                                    |  |

RARE Modules Balance High Bandwidth Cross-Channel I/O with Processing to Maximize Performance

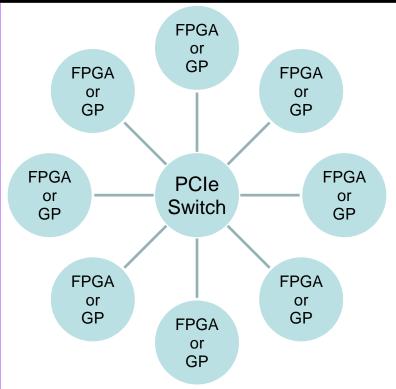

# Fabric Communication without Dedicated Switch Cards

- PCIe switches built into modular architecture

- End points can be FPGAs or General Purpose Processors

- FPGAs also interconnect with low latency, high bandwidth across the 3D topology

- LVDS

- SerDes

#### Integrated Health and Status Monitoring

- I<sup>2</sup>C network of microcontrollers distributed throughout architecture for health and status

- ADCs built into microcontrollers monitor voltages, currents, and temperatures

- Sequences power supplies and protect modules in event of supply issues or overheating

- Microcontrollers can shut down modules or system when tolerances are not within defined limits

- Fully programmable

### Software Development Kit

- Leverages open source

- Avoids sole source proprietary operating systems

- Lower TOC

- Can be tailored by user

- SDK handles module communication protocols and data movement between processors and FPGAs

- Linux kernel

- Fedora x86-64 gcc cross compiler tool chain

- U-Boot boot loader

- Core root file system

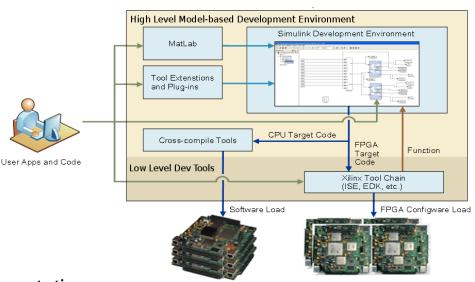

### Model-Based Programming

- Code wrappers encapsulate modules and enable MATLAB® / Simulink® tool flows for VHDL and C code development

- Model desired algorithms and functionality

- Map functions onto computing elements hosted on RARE modules

- Define interfaces between elements

- Generate embedded application code

#### Benefits

- Gain insight into behavior of complex algorithms

- Eliminate need for different tool flows and skill sets

- Quickly optimize the approach and converge on a solution

- Model also serves as a test bench to verify implementation

Enables quick turn from algorithmic concept and simulation to implementation

## Packaging Examples

#### **Platform-Ready Deployment**

- Fits specific platform installation envelopes

- Tight physical integration with antenna and RF subsystems

#### **Tailored Box-Level Solutions**

- Supports variety of module counts

- System level interfaces can be brought out to panel bulkheads (digital and analog)

#### **Standard 19" Rack Mount Enclosure**

- Supports variety of module counts based upon chassis height and depth

- System level interfaces can be brought out to panel bulkheads (digital and analog)

#### Flexible Interconnections for Form Fitting SWaP

- Flexible cable-based connections

- Fully customizable cable lengths

- Increases bandwidth for stacked systems

- Right angle and straight connectors available

- Facilitates module replacement within mesh

### **Example Applications**

- RARE architecture is being utilized by multiple DoD agencies to meet C-SWaP within challenging installation footprints

- Two examples

- Programmable MIMO radar transmit / receive system

- Sense and Avoid radar for UAVs

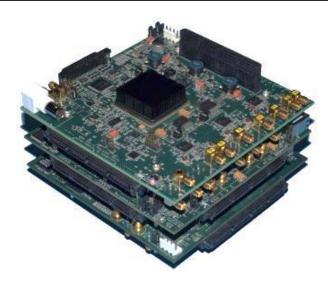

### Example 1: Multichannel DREX

- Programmable MIMO radar transmit / receive system

- Uses three COTS RARE modules

- 2x exciter channels (1 GHz)

- 10x receive channels (160 MSPS)

- 3x Virtex-6 FPGAs

- 1x PPC

- 2x 1GbE

- Electronics: 6.25" x 6.25" x 4"

- Dual 10GbE can be supported through the addition of one more module

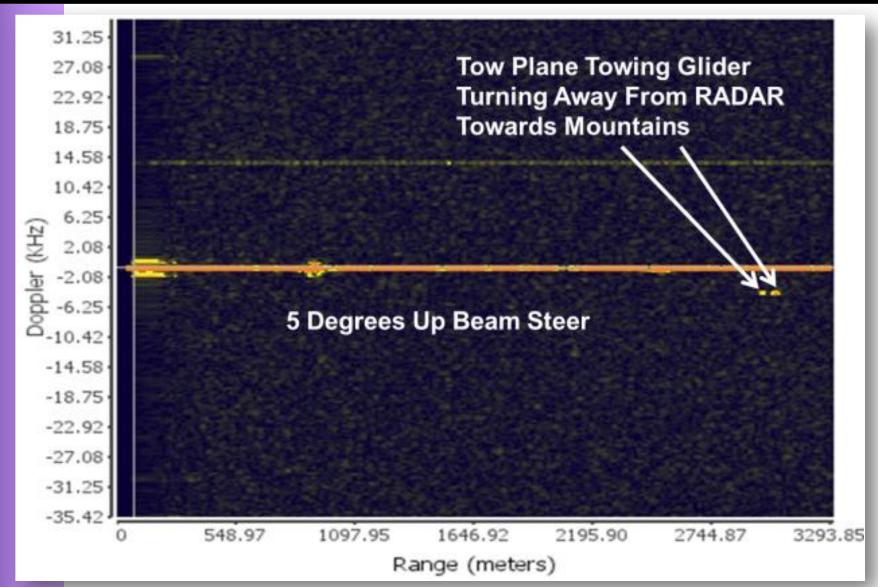

### Example 2: Sense and Avoid Radar

- Autonomous sense and avoid capability needed in unmanned aerial systems (UAS)

- Addresses safety and compliance concerns which prevent UAS from operating freely within national airspace

- Limits ability for UAS to help with

- Boarder patrol

- Weather monitoring

- Wildlife monitoring

- Search and rescue

- Local law enforcement

- Disaster relief / emergency response

- UAS platforms typically very SWaP constrained

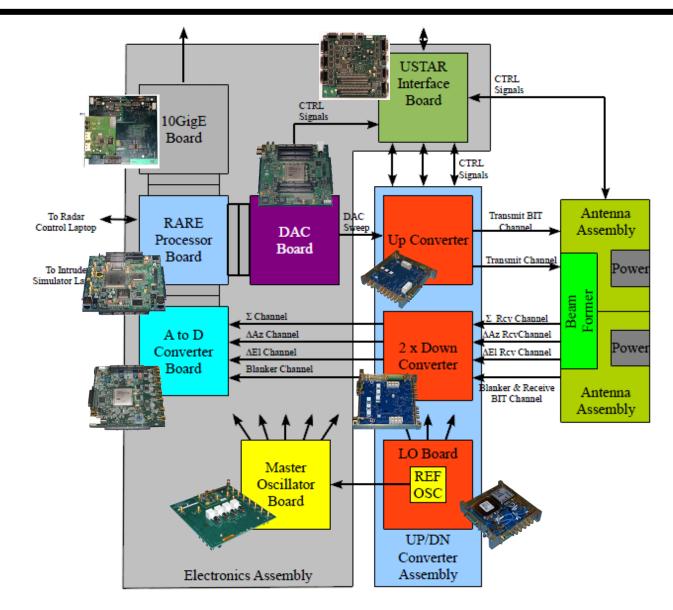

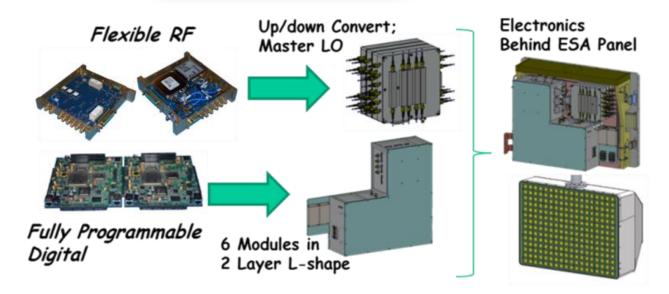

### RARE: Enabling Technology for Radar

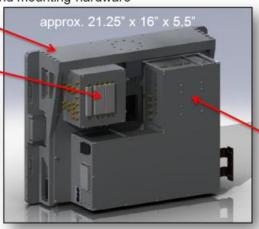

### Tight Integration onto Phased Array

#### Antenna Sub-Assembly

Includes heat sink and mounting hardware

#### RF Sub-Assembly Up converter

Down converters LO synthesis RF filters

**Digital Electronics Sub-Assembly** 6 computing modules in 2 layers (capacity = 9 in 3 layers)

#### RARE-Enabled Search/Track Radar

### Summary

- RARE enables high performance embedded computing in form-factor challenged installation envelopes

- Heterogeneous

- Scalable modularity

- 3D connectivity

- Graphical programming methodology facilitates rapid integration and deployment

- Solutions can be made less costly and more scalable in finer-grain increments than architectures employing legacy backplanes

- Award winning technology currently being utilized in multiple DoD programs

### Acknowledgements

CEI would like to thank MDA, NRL, ONR, and NSWC for their support and guidance of the RARE SBIR Phase I and II development program

#### **Thank You!**

For more information please contact:

Michael J. Bonato

Colorado Engineering, Inc.

michael.bonato@coloradoengineeringinc.com

719-388-8582 (office)

www.coloradoengineeringinc.com

# Colorado Engineering Overview

- Company mission

- Engineering excellence

- Rapid response

- Low cost

- Founded 2003

- Located in Colorado Springs, CO

- No outside investment

- Woman-owed small business (8m)

- Facility Clearance

- Winner of Tibbetts and Nunn-Perry awards

- Recognized industry leaders in MOSA applications

- 30 Phase I/II SBIR & STTR awards

- Over 37 technologies deployed in DoD and Government systems