POWERING THE NEW ENGINEER TO TRANSFORM THE FUTURE

Department of Electrical & Computer Engineering

# Synthesis of Hardware Sandboxes for Trojan Mitigation in Systems on Chip

Christophe Bobda, Taylor Whitaker, Joel Mandebi Mbongue and Sujan Kumar Saha

# Agenda

- Motivation

- Hardware Sandbox Concept

- Background and Automata Definitions

- Automatic Sandbox Generation

- Evaluation and Case Study

- Summary and Future Work

# **Motivation**

UF

- Industries rely on 3<sup>rd</sup> Party IPs (3PIPs) while designing SoC

- 3PIPs are often black box to integrator

- A 3PIP may contain hardware Trojan which can do malicious activities while running the system

- A 3PIP can be a security threat for a system

- Industries rely on mutual verification of IP security concerns

Reference: Security Assurance Guidance for Third-Party IP Sherman, B., Borza, M., Rosenberg, B. et al. J Hardw Syst Secur (2017) 1: 38.

# **Motivation**

UF

- Manual verification is a tedious job for security experts of 3PIP provider and integrator

- It may be time consuming depending on complexity of the IP. Hence, may lead to integration delay

- Highly dependent on security experts. So, possibility of existence of unidentified threat in the IP

- Current Hardware level solutions do not include automatic security policies generation

- No resource virtualization is present in literature and hence proper hardware isolation is not maintained

UF

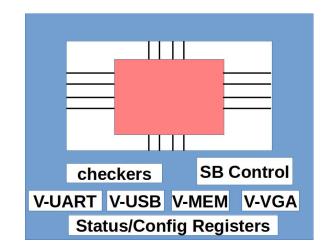

### Hardware Sandbox Concept

- Non-trusted IPs are kept in a Sandbox with guards so that malicious activities cannot be performed by the IPs to the rest of the system

- A opposite concept of ARM Trustzone where trusted components are kept in a trusted zone.

- Virtualization of resources are provided to the IP to maintain proper isolation (e.g. V-UART, V-USB, V-MEM etc.)

Figure 1: Structure of the Hardware Sandbox

UF

# **Background and Definition**

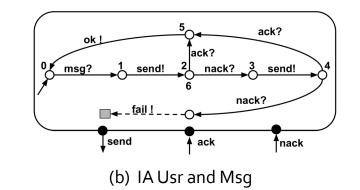

**Definition 1** (Interface Automaton). An Interface Automaton is a tuple  $S = \langle Q, q_0, q_f, A^I, A^O, A^H, \delta \rangle$  where:

- Q is a finite set of states with q<sub>0</sub> ∈ Q being the initial state and q<sub>f</sub> ⊆ Q being the set of final states;

- $A = A^{I} \cup A^{O} \cup A^{H}$  is the set of actions, where  $A^{I}, A^{O}$ and  $A^{H}$  are pairwise disjoint finite sets of input, output, and hidden actions, respectively.

- δ ⊆ Q×A×Q is the transition relation that is required to be input deterministic (i.e. (q, a, q<sub>1</sub>), (q, a, q<sub>2</sub>) ∈ δ implies q<sub>1</sub> = q<sub>2</sub> for all a ∈ A<sup>I</sup> and q, q<sub>1</sub>, q<sub>2</sub> ∈ Q).

**Definition 2** (Interface Compositionality). Given two IA  $S = \langle Q_S, q_{0S}, q_{fS}, A_S^I, A_S^O, A_S^H, \delta_S \rangle$  and  $T = \langle Q_T, q_{0T}, q_{fT}, A_T^I, A_T^O, A_T^H, \delta_T \rangle$  and their set of share actions shared $(S,T) = A_S \cap A_T$ , we say that S and T are composable whenever shared $(S,T) = (A_S^I \cap A_T^O) \cup (A_S^O \cap A_T^I)$ .

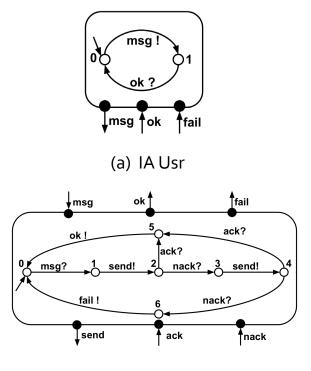

(b) IA Msg

Figure 2: User and Message automaton for packet transmission

UF

#### **Background and Definition**

**Definition 3** (Composition). The composition (product)  $S \bigotimes T$  of two composable IA S and T is defined by:

- $Q_{S \otimes T} = Q_S X Q_T$  with  $q^I 0_{S \otimes T} = (q^I 0_S, q^I 0_T)$

- $A_{S \otimes T}^{I} = A_{S}^{I} \cup A_{T}^{I} shared(S,T), A_{S \otimes T}^{O} = A_{S}^{O} \cup A_{T}^{O} shared(S,T)$  and  $A_{S \otimes T}^{H} = A_{S}^{H} \cup A_{T}^{H} \cup shared(S,T)$

- $\delta_S \otimes_T = \{(q,s), a, (q',s) | (q,a,q') \in \delta_S \land a \notin Share(S,T) \land s \in Q_T\} \bigcup \{(q,s), a, (q,s') | (s,a,s') \in \delta_T \land a \notin Share(S,T) \land q \in Q_S\} \bigcup \{(q,s), a, (q',s') | (q,a,q') \in \delta_S \land (s,a,s') \in \delta_T \land a \in Share(S,T)\}$

**Definition 4** (Illegal States). Given two IA S and T, the set Illegal(S,T) of illegal states of  $S \bigotimes T$  is defined as:  $Illegal(S,T) = \{(q,s) \in Q_S \times Q_T | \exists a \notin Share(S,T), st(a \in A_S^O(q)) \land (a \notin A_T^I(s))or(a \in A_T^O(s)) \land (a \notin A_S^I(s))\}$

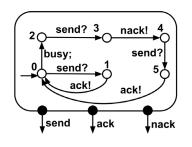

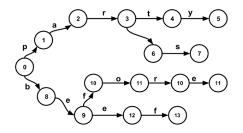

Figure 3: Video capture, compression and transmission

UF

#### **Background and Definition**

**Definition 5** (Component). A component, C, is a tuple (U,I) where U is the core function of C,  $I = \langle Q, q0, qf, A^I, A^O, A^H, \delta \rangle$  is an IA through which C interacts with other components, for instance, a messaging interface or a procedural interface.

**Definition 6** (Labeled Transition Systems). A labeled transition system (LTS) A is a tuple  $S = \langle Q, q_0, A, \delta \rangle$  where Q is a finite set of states with  $q_0 \in Q$  being the initial state, A set of observable actions called the alphabet of S,  $\delta \subseteq Q \times A \times Q$ is the transition relation. We write  $q \stackrel{\alpha}{\rightarrow} s$  when  $(q, a, s) \in \delta$ , in which case we say that a is enable in q with destination s. S is deterministic if  $\delta$  is a function, i.e.  $\forall q \in Q$  and  $a \in A$ ,  $q \stackrel{\alpha}{\rightarrow} s$  for atmost one state  $s \in Q$ , and is otherwise non-deterministic. **Definition 7** (LTS Composition). Given LTSs  $S = \langle Q_S, q_{0S}, A_S, \delta_S \rangle$  and  $T = \langle Q_T, q_{0T}, A_T, \delta_T \rangle$ , the composition S || T is an LTS with states  $Q_S \times Q_T$ , initial state  $(q_{0S}, q_{0T})$ , alphabet  $A_S \cup A_T$ , and a transition relation defined by the rules (including the symmetric versions):  $\frac{q \stackrel{\alpha}{\to} q'; q' \notin \Pi; a \notin A_T}{(q,s) \stackrel{\alpha}{\to} (q',s)}$ ,  $\frac{q \stackrel{\alpha}{\to} q'; s \stackrel{\alpha}{\to} s'; q', s' \notin \Pi}{(q,s) \stackrel{\alpha}{\to} (q',s)}$ , and  $\frac{q \stackrel{\alpha}{\to} (\pi \in \Pi)}{(q,s) \stackrel{\alpha}{\to} (\pi \in \Pi)}$

UF

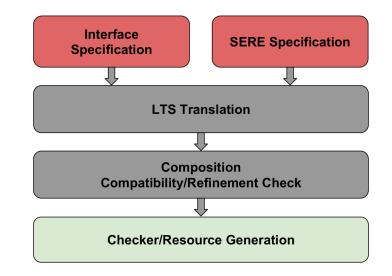

#### **Automatic Sandbox Generation**

- Component Authentication Process for Sandboxed Layouts (CAPSL) - An automatic Sandbox generation framework

- IP functionality, Interface and access rules are defined in Property Specification Language (PSL)

- Interface automata and SERE expressions are given as input

- Level Transition Systems (LTS) translation is done using PSL rules

- Hardware Sandbox is generated in VHDL

#### Figure 3: Sandbox generation in CAPSL

# **LTS Generation**

UF

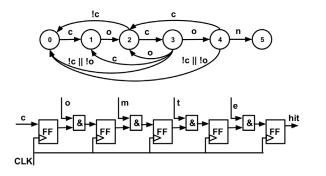

- While doing LTS generation, two optimization is done: Pattern matching and one-hot coding

- One-hot coding reduces the need of additional logic for multiple interface inputs

- Transition diagram of "cocon" automaton shows many backward transitions

- Regular expression uses 3 FFs and logic and routing for backword transition

- Our optimijization requires 5 FFs and 5 AND gates but no backward edge, hence more compact design

Figure 4: One-hot implementation of "cocon" - automaton

UF

## **Evaluation Platform**

- Digilent Zybo FPGA board with Zynq-7000 FPGA

- Trust-hub bechmarks

- UART for external connection

- RS232-based hardware Trojans

UF

## **Case Study Result**

- Resource overhead is negligible

- The overhead is absolute, will not grow with the size of the circuit

- Delay overhead shows no slowdown for adding Hardware Sandbox

- Overhead for virtualization is also very less

| Design | Trojan Class | Checker Type   | Area Overhead   | Delay Overhead |

|--------|--------------|----------------|-----------------|----------------|

| T-300  | Info leak    | Cycle Sequence | 243 LUT (1.38%) | -0.729 ns      |

| T-400  | Info leak    | Cycle Sequence | 278 LUT (1.58%) | -0.046 ns      |

| T-500  | DoS          | Cycle Sequence | 269 LUT (1.52%) | -0.174 ns      |

| T-900  | DoS          | Cycle Sequence | 265 LUT (1.51%) | -0.149 ns      |

TABLE I: Evaluation of our hardware checkers with various designs from the Trust-Hub (www.trust-hub.com) benchmark.

| Virtual Resource    | Area Overhead   | Delay Overhead |

|---------------------|-----------------|----------------|

| VGA (V-VGA)         | 23 LUT (0.13%)  | -0.037 ns      |

| RS232-UART (V-UART) | 120 LUT (0.68%) | -0.567 ns      |

TABLE II: Evaluation of our virtual resources.

# Summary

UF

- Our proposed design flow can generate Hardware Sandbox in VHDL language for an IP or multiple of IPs

- It reduces time and cost of Sandbox designing

- Optimization is done for compact sandbox generation

- It insures 100% detection of unexpected behaviour of IPs

- The overhead is minimal

#### **UF** Herbert Wertheim College of Engineering UNIVERSITY of FLORIDA

#### smartsystems.ece.ufl.edu

POWERING THE NEW ENGINEER TO TRANSFORM THE FUTURE